Adv. Func. Mater.:基于二维异质结的可重构逻辑存储器和多语言人工突触

QQ学术交流群:1092348845

详细介绍

研究背景

内存计算架构被认为是超越传统互补金属氧化物半导体(CMOS)技术的最有前景的技术之一。传统的冯·诺依曼计算架构由于逻辑和存储模块之间的瓶颈而面临着提供更高性能和更低功耗的巨大挑战。内存计算器件,诸如人造突触器件和基于非易失性器件的三进制内容可寻址存储器(TCAM)之类,成为了未来电子学中有潜力的候选者,并且近年来引起了极大的研究关注。到目前为止,在实验中已经实现了多种非易失性器件,包括电阻随机存取存储器(RRAM),相变存储器(PCM),铁电场效应晶体管(FeFET)和磁随机存取存储器(MRAM)。由于能带结构的多样性,2D范德华异质结在存储器和逻辑器在内的多功能器件中表现出巨大潜力。此外,基于2D材料的人工突触器件也已被证明具有多功能人工神经网络(ANN)和神经形态计算的潜力。然而,在先前展示的关于非易失性多值逻辑运算和多语言突触运算的器件中仍然缺乏多样性和多功能性。基于新兴的2D材料及其异质结可以探索新型电子器件,为逻辑存储器件的发展提供了新思路。

成果介绍

有鉴于此,近日,华中科技大学吴燕庆教授团队报道了基于直接带隙材料黑磷(BP)和二硫化铼(ReS2)的2D范德华异质结用于非易失性三进制逻辑运算,其中超薄黑磷氧化层用作电荷俘获以及带间隧穿层。基于该异质结的人工电子突触被证明可以通过改变输入基极电压来实现三语突触响应。此外,利用手写数字数据,基于电子突触阵列的人工神经网络仿真可以获得91.3%的高识别精度。这项工作为基于新颖的2D异质结实现多功能非易失性逻辑逻辑存储应用提供了一条途径,文章以“Reconfigurable Logic-in-Memory and Multilingual Artificial Synapses Based on 2D Heterostructures”为题发表在著名期刊Advanced Functional Materials上

图文导读

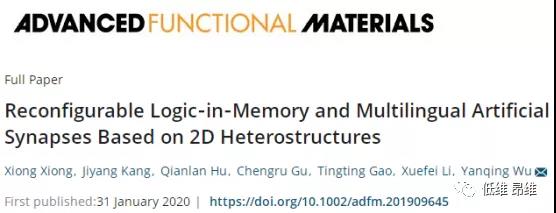

图1. 范德华异质结和器件表征。(a)BP/ReS2异质结器件的示意图以及结区界面的晶格截面示意图。漏极沉积在BP层上,源极沉积在ReS2层上。(b)BP/ReS2界面的横截面高分辨TEM图像,可以观察到约4 nm的POx层。(c)器件的光学显微图像。(d)BP,BP/ReS2重叠和ReS2区域的拉曼光谱。(e,f)300 K和4.3 K时具有不同Vd和Vg偏置的BP/ReS2异质结的电流。

图1a给出了BP/ReS2异质结器件的示意图,机械剥离的BP和ReS2薄片转移到25 nm HfO2覆盖的硅衬底上,通过EBL蒸镀20/40 nm的Ni/Au形成源漏电极。BP/ReS2异质结截面的高分辨率TEM如图1b所示,其中可以看到BP和ReS2的高度结晶分层晶格,并且BP和ReS2之间有4 nm POx层。图1c显示了器件的光学显微图像,通过AFM确定BP和ReS2的厚度分别约为10和7 nm。BP/ReS2异质结三个位置(包括BP区,ReS2区和结区)的拉曼光谱如图1d所示,结区的拉曼光谱是两种材料的特征峰的叠加。图1e和f给出了BP/ReS2异质结在300 K和4.3 K下漏极电流Id作为漏极和栅极电压的函数的成像。在BP端施加从-3至3 V的漏极电压,并且ReS2源极端始终接地。由于在各种电压偏置下能带对准条件不同,因此漏极电流表现出非单调依赖性,并且在-4至4 V的Vg和-3至3 V的Vd情况下具有连续可调性,这在4.3 K时更明显。这些变化可以归因于能带排列移动,其中异质结结区从ReS2为主的n-p结变为BP为主的n-p结和n-n结。

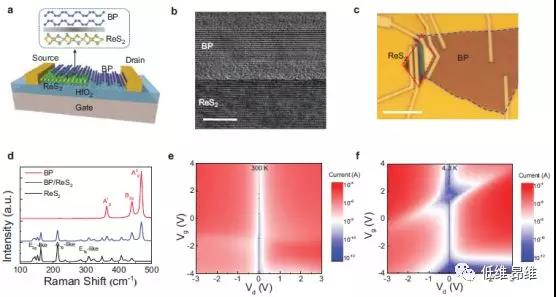

图2. 三进制逻辑电路。(a)在Vd=1 V时BP FET和BP/ReS2异质结FET的转移特性。(b)Vdd为0.1至2 V时,BP/ReS2异质结串联BP FET的三进制反相器的Vout相对于Vin的变化。插图:三进制反相器的电路示意图。(c)反相器1 Hz下的三进制输入波形与三进制逻辑输出波形。(d)零偏压时,热平衡状态下异质结的能带图。(e-h)负Vd偏置和正Vd偏置时异质结的能带图。

与传统的二进制逻辑相比,多值逻辑器件可以以较小的磁盘空间实现更高的数据密度。通过串联使用BP/ReS2异质结FET和BP FET,实现了基于2D材料的三进制逻辑电路。图2a给出了漏极电压为1 V时BP FET和BP/ReS2异质结FET的单独转移特性曲线。异质结的负跨导区域源于带间隧穿机制,其中漏极偏置将BP的能带向下弯曲,形成高隧穿效率区域。主电流通过异质结从ReS2的n型输运变为n型空穴隧穿,随着栅极偏置的增加表现出下降的趋势,在负跨导区域之外,栅极偏置进一步增大,由于强n–n结,电流将再次上升。图2b中绘制了Vout对于Vin的三进制反相器(Vdd为0.2至2 V),输出特性显示三个不同的逻辑状态区域,包括输入电压Vin<-2 V的“逻辑1”,-2 V

图3. 非易失性三进制逻辑电路。(a)在负Vg偏置和正Vg偏置条件下载流子俘获和去俘获过程的能带示意图。(b)Vdd=1 V时,三进制逻辑反相器的典型双扫电压传输特性。(c)在不同的Vin脉冲宽度下,具有±4 V的固定Vin脉冲幅度且Vin_base=-1.8 V,输出在逻辑1/2到逻辑1之间切换。(d)在Vin_base=0.3 V的不同Vin脉冲宽度下,输出在逻辑0和逻辑1/2之间切换。

BP自然氧化在表面形成电荷俘获层,表现为电荷保留层(图3a)。三进制逻辑反相器的电压传输曲线在双电压扫描下也表现出明显的滞后现象(图3b),可以看出,根据电压扫描方向可以获得两个单独的输出状态,在Vin=-1.8 V时显示“1/2”和“1”,在Vin=0.3 V时显示“0”和“1/2”。在固定Vin_base=-1.8 V的条件下,通过Vin脉冲的输出特性可以更好地观察到“1/2”和“1”两电平输出(图3c)。当脉冲宽度从50 ms减小到1 ms时,“逻辑1”显示很小的变化,但“逻辑1/2”的输出电压相应增加。同样,也可以通过在固定Vin_base=0.3 V时的Vin脉冲来切换“0”和“1/2”两电平输出,逻辑“0”变化很小,但“逻辑1/2”的输出电压随脉冲宽度的减小而增加(图3d)。脉冲切换的结果表明,非易失性三进制逻辑反相器可以在各种输入条件下工作。

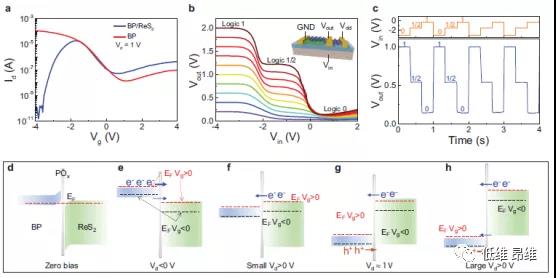

图4. 基于BP/ReS2异质结的人工三语突触。(a)生物突触和人工突触的示意图。(b)对于–2、0和2 V的三种不同Vg_base条件,输入端上4 V输入脉冲(10 ms)的PSC响应。(c)在不同的Vg和Vd下,漏极电流的测量方向依赖性。三种不同的Vg条件显示出变化趋势,对应于(b)中的1-3点。(d)在300 K时Vd=1 V的情况下,4 V输入脉冲(10 ms)的突触权重随不同Vg_base的变化。(e)在300 K时Vd=1 V和Vg_base=0 V的情况下,4 V输入脉冲的突触权重随不同脉冲宽度的变化。(f)使用Vd=0.5 V的50个增强(4 V,100 μs)和抑制(-4 V,10 μs)突触前输入,突触异质结的长时程增强和抑制。(g)三层(一个隐藏层)神经网络的示意图。(h)具有实验和理想数值的大小手写数字图像的识别精度。

人工突触可用于人工神经网络(ANN)和神经形态计算,这对于低能耗的下一代计算架构具有巨大的应用潜力。图4a给出了生物和人工电子突触的示意图,栅极端作为突触前输入,而源极端作为突触后输出。图4b显示了在三个静电Vg偏置条件下,Vg脉冲幅度为4 V的突触行为。通过以固定的Vd=1 V,调节基极的偏置电压Vg(2,0,-2 V),突触后电流(PSC)表现出长时程兴奋和长时程抑制反应。绘制了作为Vd和双扫频Vg的漏极电流图,对应于如图4c所示的不同突触行为。如前所述,正输入脉冲会将电子注入POx层,导致Vg_base=0 V时PSC增大,而Vg_base=+2/-2 V时PSC减小。如图4d中器件对Vg_base的突触行为依赖性所示,当突触前输入基极电压为-3至3 V时,三个区域从抑制变为兴奋,再回到抑制响应,表现出三语言响应特性,同时在Vd=1 V的相同4 V脉冲幅度下,突触权重可调。三语言响应的独特可调谐性源自BP/ReS2异质结器件的反双极性,同样可以扩展到其他TMD材料中。

图4e显示了振幅为4 V,基值为0 V的兴奋性PSC的权重变化与突触前输入脉冲的关系。随着突触前输入脉冲宽度从1 μs增加到100 ms,随着越来越多的载流子被捕获到POx俘获层中,突触权重变化表现出从5%到超过≈104%的单调增加趋势,从而对费米能级移动产生了更强的影响。最大的长时程突触权重变化达到23300%,超过了先前报道的结果。图4f显示了通过交替输入50个正(4 V,100μs)和50个负(-4 V,10μs)栅极电压脉冲输入而产生的PSC,表现出对生物突触的长时程增强(LTP)和长时程抑制(LTD)的可重复和稳定响应。图4g显示了用于手写数字的神经网络示意图,其中包含784个输入神经元,300个隐藏神经元和10个输出神经元,用于28×28输入像素和10个输出分类。非易失性异质结器件被用作网络中权重的存储,并且在反向传播算法的过程中,采用人工突触电导的变化作为权重更新。如图4h所示,使用理想浮点数值精度对图4f中长期可塑性实验结果的两个数据集进行模拟的测试识别精度,小数字和大数字的识别精度最终可以达到≈91.3%和89.5%,低于理想的数字精度≈96.7%和98.1%。精度差异来自LTP和LTD过程中的非线性和不对称电导变化,可以通过优化的电荷俘获层进一步改善。

总结与展望

本文构筑了基于BP和ReS2的多功能范德华异质结,实现了非易失性三进制逻辑反相器和可调的多语言人工神经突触,突触权重变化达到创纪录的104%以上。同时基于异质结器件的手写数字识别的神经网络仿真也已成功实现,识别精度约为90%。这些发现为基于新颖的2D异质结实现多功能非易失性逻辑逻辑存储应用提供了一条途径,表明2D逻辑存储器件有望用于未来的高性能、低功耗运算。

文献信息

Reconfigurable Logic‐in‐Memory and Multilingual Artificial Synapses Based on 2D Heterostructures (Adv. Func. Mater., 2020, DOI: 10.1002/adfm.201909645)

文献链接:https://onlinelibrary.wiley.com/doi/10.1002/adfm.201909645

- 上一款: Nat. Electron.:由非易失性铁电

- 下一款: Nature大子刊:天然微米粒子调节衰老群体

Copyright © 北京北科新材科技有限公司

京ICP备16054715-2号

公司简介

公司简介