��ѯ���ߣ�

17715390137

18101240246

18914047343

�ʼ���mxenes@163.com

ɨ���ע�����������ںţ�

������Fronrier

��ע�������½���ϵ���ǣ�

������ҵ�š�

רҵ��������

�����

�ڴ����ܹ�����Ϊ�dz�Խ��ͳ��������������뵼�壨CMOS������������ǰ���ļ���֮һ����ͳ�ķ롤ŵ��������ܹ��������ʹ洢ģ��֮���ƿ�����������ṩ�������ܺ����ĵľ���ս���ڴ������������������ͻ�������ͻ��ڷ���ʧ�����������������ݿ�Ѱַ�洢����TCAM��֮�࣬��Ϊ��δ������ѧ����DZ���ĺ�ѡ�ߣ����ҽ����������˼�����о���ע����ĿǰΪֹ����ʵ�����Ѿ�ʵ���˶��ַ���ʧ���������������������ȡ�洢����RRAM�������洢����PCM�������糡ЧӦ����ܣ�FeFET���ʹ������ȡ�洢����MRAM���������ܴ��ṹ�Ķ����ԣ�2D���»����ʽ��ڴ洢�����������ڵĶ�������б��ֳ���DZ�������⣬����2D���ϵ��˹�ͻ������Ҳ�ѱ�֤�����ж���˹������磨ANN��������̬�����DZ����Ȼ��������ǰչʾ�Ĺ��ڷ���ʧ�Զ�ֵ������Ͷ�����ͻ���������������Ȼȱ�������ԺͶ���ԡ��������˵�2D���ϼ������ʽ����̽�����͵���������Ϊ���洢�����ķ�չ�ṩ����˼·��

�ɹ�����

�м��ڴˣ����գ����пƼ���ѧ����������Ŷӱ����˻���ֱ�Ӵ�϶���Ϻ��ף�BP���Ͷ���画�ReS2����2D���»����ʽ����ڷ���ʧ�������������㣬���г�������������������ɷ����Լ����������㡣���ڸ����ʽ���˹�����ͻ����֤������ͨ���ı����������ѹ��ʵ������ͻ����Ӧ�����⣬������д�������ݣ����ڵ���ͻ�����е��˹������������Ի��91.3���ĸ�ʶ�ȡ������Ϊ������ӱ��2D���ʽ�ʵ�ֶ�ܷ���ʧ�������洢Ӧ���ṩ��һ��;���������ԡ�Reconfigurable Logic-in-Memory and Multilingual Artificial Synapses Based on 2D Heterostructures��Ϊ�ⷢ���������ڿ�Advanced Functional Materials��

ͼ�ĵ���

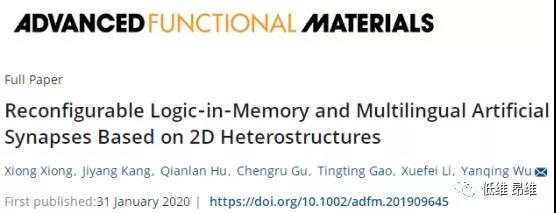

ͼ1. ���»����ʽ��������������a��BP/ReS2���ʽ�������ʾ��ͼ�Լ���������ľ������ʾ��ͼ��©��������BP���ϣ�Դ��������ReS2���ϡ���b��BP/ReS2����ĺ����߷ֱ�TEMͼ���Թ۲쵽Լ4 nm��POx�㡣��c�������Ĺ�ѧ��ͼ��d��BP��BP/ReS2�ص���ReS2������������ס���e��f��300 K��4.3 Kʱ���в�ͬVd��Vgƫ�õ�BP/ReS2���ʽ�ĵ�����

ͼ1a������BP/ReS2���ʽ�������ʾ��ͼ����е�����BP��ReS2��Ƭת�Ƶ�25 nm HfO2���ǵĹ�ĵ��ϣ�ͨ��EBL����20/40 nm��Ni/Au�γ�Դ©�缫��BP/ReS2���ʽ����ĸ߷ֱ���TEM��ͼ1b��ʾ�����п��Կ���BP��ReS2�ĸ߶Ƚᾧ�ֲ㾧����BP��ReS2֮����4 nm POx�㡣ͼ1c��ʾ�������Ĺ�ѧ��ͼ��ͨ��AFMȷ��BP��ReS2�ĺ�ȷֱ�ԼΪ10��7 nm��BP/ReS2���ʽ�����λ�ã�����BP����ReS2���ͽ�����������������ͼ1d��ʾ���������������������ֲ��ϵ�������ĵ��ӡ�ͼ1e��f������BP/ReS2���ʽ���300 K��4.3 K��©������Id��Ϊ©����դ����ѹ�ĺ����ij�����BP��ʩ�Ӵ�-3��3 V��©����ѹ������ReS2Դ����ʼ�սӵء������ڸ��ֵ�ѹƫ�����ܴ���������ͬ�����©���������ֳ��ǵ��������ԣ�������-4��4 V��Vg��-3��3 V��Vd����¾��������ɵ��ԣ�����4.3 Kʱ�����ԡ���Щ�仯���Թ������ܴ������ƶ����������ʽ������ReS2Ϊ����n-p���ΪBPΪ����n-p���n-n�ᡣ

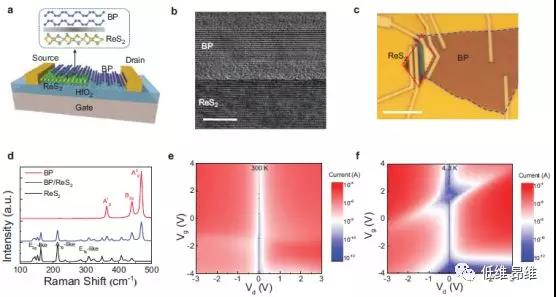

ͼ2. ����������·����a����Vd=1 VʱBP FET��BP/ReS2���ʽ�FET��ת�����ԡ���b��VddΪ0.1��2 Vʱ��BP/ReS2���ʽᴮ��BP FET�������Ʒ�������Vout�����Vin�ı仯����ͼ�������Ʒ������ĵ�·ʾ��ͼ����c��������1 Hz�µ����������벨������������������Ρ���d����ƫѹʱ����ƽ��״̬�����ʽ���ܴ�ͼ����e-h����Vdƫ�ú���Vdƫ��ʱ���ʽ���ܴ�ͼ��

�봫ͳ�Ķ���������ȣ���ֵ�����������Խ�С�Ĵ��̿ռ�ʵ�ָ��ߵ������ܶȡ�ͨ������ʹ��BP/ReS2���ʽ�FET��BP FET��ʵ���˻���2D���ϵ�����������·��ͼ2a������©����ѹΪ1 VʱBP FET��BP/ReS2���ʽ�FET�ĵ���ת���������ߡ����ʽ�ĸ��絼����Դ�ڴ����������ƣ�����©��ƫ�ý�BP���ܴ������������γɸ�����Ч������������ͨ�����ʽ��ReS2��n�����˱�Ϊn�Ϳ�Ѩ����������դ��ƫ�õ����ӱ��ֳ��½������ƣ��ڸ��絼����֮�⣬դ��ƫ�ý�һ����������ǿn�Cn�ᣬ�������ٴ�������ͼ2b�л�����Vout����Vin�������Ʒ�������VddΪ0.2��2 V�������������ʾ������ͬ����״̬�����������ѹVin<-2 V�ġ���1����-2 V

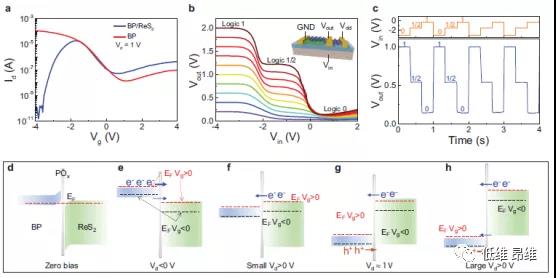

ͼ3. ����ʧ������������·����a���ڸ�Vgƫ�ú���Vgƫ�������������ӷ����ȥ������̵��ܴ�ʾ��ͼ����b��Vdd=1 Vʱ�����������������ĵ���˫ɨ��ѹ�������ԡ���c���ڲ�ͬ��Vin��������£����С�4 V�Ĺ̶�Vin���������Vin_base=-1.8 V���������1/2����1֮���л�����d����Vin_base=0.3 V�IJ�ͬVin��������£��������0����1/2֮���л���

BP��Ȼ�����ڱ����γɵ�ɷ���㣬����Ϊ��ɱ����㣨ͼ3a�������������������ĵ�ѹ����������˫��ѹɨ����Ҳ���ֳ����Ե��ͺ�����ͼ3b�������Կ��������ݵ�ѹɨ�跽����Ի���������������״̬����Vin=-1.8 Vʱ��ʾ��1/2���͡�1������Vin=0.3 Vʱ��ʾ��0���͡�1/2�����ڹ̶�Vin_base=-1.8 V�������£�ͨ��Vin�����������Կ��Ը��õع۲쵽��1/2���͡�1������ƽ�����ͼ3c������������ȴ�50 ms��С��1 msʱ������1����ʾ��С�ı仯��������1/2���������ѹ��Ӧ���ӡ�ͬ����Ҳ����ͨ���ڹ̶�Vin_base=0.3 Vʱ��Vin�������л���0���͡�1/2������ƽ���������0���仯��С��������1/2���������ѹ��������ȵļ�С�����ӣ�ͼ3d���������л��Ľ������������ʧ���������������������ڸ������������¹�����

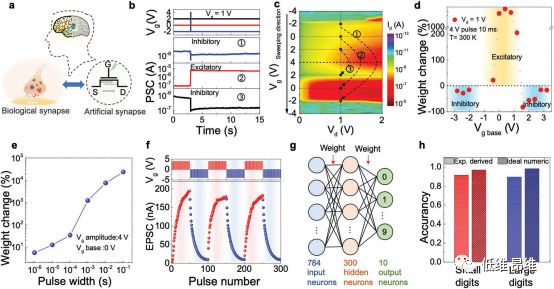

ͼ4. ����BP/ReS2���ʽ���˹�����ͻ������a������ͻ�����˹�ͻ����ʾ��ͼ����b�����ڨC2��0��2 V�����ֲ�ͬVg_base�������������4 V�������壨10 ms����PSC��Ӧ����c���ڲ�ͬ��Vg��Vd�£�©�������IJ������������ԡ����ֲ�ͬ��Vg������ʾ���仯���ƣ���Ӧ�ڣ�b���е�1-3�㡣��d����300 KʱVd=1 V������£�4 V�������壨10 ms����ͻ��Ȩ���治ͬVg_base�ı仯����e����300 KʱVd=1 V��Vg_base=0 V������£�4 V���������ͻ��Ȩ���治ͬ������ȵı仯����f��ʹ��Vd=0.5 V��50����ǿ��4 V��100 ��s�������ƣ�-4 V��10 ��s��ͻ��ǰ���룬ͻ�����ʽ�ij�ʱ����ǿ�����ơ���g�����㣨һ�����ز㣩�������ʾ��ͼ����h������ʵ���������ֵ�Ĵ�С��д����ͼ���ʶ�ȡ�

�˹�ͻ���������˹������磨ANN��������̬���㣬����ڵ��ܺĵ���һ������ܹ����о��Ӧ��DZ����ͼ4a������������˹�����ͻ����ʾ��ͼ��դ������Ϊͻ��ǰ���룬��Դ������Ϊͻ���������ͼ4b��ʾ������������Vgƫ�������£�Vg�������Ϊ4 V��ͻ����Ϊ��ͨ���Թ̶���Vd=1 V�����ڻ�����ƫ�õ�ѹVg��2��0��-2 V����ͻ���������PSC�����ֳ���ʱ���˷ܺͳ�ʱ�����Ʒ�Ӧ����������ΪVd��˫ɨƵVg��©������ͼ����Ӧ����ͼ4c��ʾ�IJ�ͬͻ����Ϊ����ǰ����������������Ὣ����ע��POx�㣬����Vg_base=0 VʱPSC����Vg_base=+2/-2 VʱPSC��С����ͼ4d��������Vg_base��ͻ����Ϊ��������ʾ����ͻ��ǰ���������ѹΪ-3��3 Vʱ��������������Ʊ�Ϊ�˷ܣ��ٻص�������Ӧ�����ֳ���������Ӧ���ԣ�ͬʱ��Vd=1 V����ͬ4 V��������£�ͻ��Ȩ�ؿɵ�����������Ӧ�Ķ��ؿɵ�г��Դ��BP/ReS2���ʽ������ķ�˫���ԣ�ͬ��������չ������TMD�����С�

ͼ4e��ʾ�����Ϊ4 V����ֵΪ0 V���˷���PSC��Ȩ�ر仯��ͻ��ǰ��������Ĺ�ϵ������ͻ��ǰ����������ȴ�1 ��s���ӵ�100 ms������Խ��Խ��������ӱ�����POx������У�ͻ��Ȩ�ر仯���ֳ���5����������104���ĵ����������ƣ��Ӷ��Է����ܼ��ƶ������˸�ǿ��Ӱ�졣���ij�ʱ��ͻ��Ȩ�ر仯�ﵽ23300������������ǰ�����Ľ����ͼ4f��ʾ��ͨ����������50������4 V��100��s����50������-4 V��10��s��դ����ѹ���������������PSC�����ֳ�������ͻ���ij�ʱ����ǿ��LTP���ͳ�ʱ�����ƣ�LTD���Ŀ��ظ����ȶ���Ӧ��ͼ4g��ʾ��������д���ֵ�������ʾ��ͼ�����а���784��������Ԫ��300��������Ԫ��10�������Ԫ������28��28�������غ�10��������ࡣ����ʧ�����ʽ�����������������Ȩ�صĴ洢�������ڷ����㷨�Ĺ����У������˹�ͻ���絼�ı仯��ΪȨ�ظ��¡���ͼ4h��ʾ��ʹ�����븡����ֵ���ȶ�ͼ4f�г��ڿ�����ʵ�������������ݼ�����ģ��IJ���ʶ�ȣ�С���ֺʹ����ֵ�ʶ�����տ��Դﵽ��91.3����89.5����������������־��ȡ�96.7����98.1�������Ȳ�������LTP��LTD�����еķ����ԺͲ��ԳƵ絼�仯������ͨ���Ż��ĵ�ɷ�����һ�����ơ�

�ܽ���չ��

���Ĺ����˻���BP��ReS2�Ķ�ܷ��»����ʽᣬʵ���˷���ʧ�����������������Ϳɵ��Ķ������˹���ͻ����ͻ��Ȩ�ر仯�ﵽ����¼��104�����ϡ�ͬʱ�������ʽ���������д����ʶ������������Ҳ�ѳɹ�ʵ�֣�ʶ��ԼΪ90������Щ����Ϊ������ӱ��2D���ʽ�ʵ�ֶ�ܷ���ʧ�������洢Ӧ���ṩ��һ��;��������2D���洢������������δ���ĸ����ܡ��������㡣

������Ϣ

Reconfigurable Logic�\in�\Memory and Multilingual Artificial Synapses Based on 2D Heterostructures (Adv. Func. Mater., 2020, DOI: 10.1002/adfm.201909645)

�������ӣ�https://onlinelibrary.wiley.com/doi/10.1002/adfm.201909645

|

|

|

|

| ��ά����Frontier | �������ײ���ǰ�� | MXenes Frontier | ����ҽѧFrontier |

| ��ܰ��ʾ�����������²ĿƼ�����Ӧ��Ʒ�����ڿ��У������������塣������վʾ��ͼԴ�Ի�������ͼƬ�����ο�������ʵ�ʲ��Խ��Ϊ��������Ȩ����ϵ��������ɾ������Ʒ���������ο�������ʵ��ֵΪ�� |

|

��Ȩ���� © 2019 ���������²ĿƼ�����˾

All rights reserved. ��ICP��16054715��-2 |

ɨһɨ